## 中国科学院软件研究所学术年会'2022 暨计算机科学国家重点实验室开放周

## 吴科余、吴凤鸽、赵军锁

"Optimization Strategy of Satellite Signal Processing Software based on Feiteng FT-2000 Computing Board," 2021 20th International Conference on Ubiquitous Computing and Communications (IUCC/CIT/DSCI/SmartCNS), 2021, pp. 208-215, doi: 10.1109/IUCC-CIT-DSCI-SmartCNS55181.2021.00044.

> 邮箱: keyu2020@iscas.ac.cn 电话: 18696149562

**Abstract**—At present, GPU and FPGA have become conventional acceleration methods for software. However, considering about satellite power consumption and heat dissipation, the highpower GPU hardware acceleration method is inapplicable for the on-board environment, at the mean time the lowpower FPGA acceleration will greatly increase the development cycle and development cost of application software. Therefore, the application software on the satellite needs to explore for the optimization of the code under the conditions of limited hardware. In response to the above problems, this paper focuses on the running time of the satellite signal processing software, and proposes an effective software optimization strategy. The strategy applies multiple optimization methods including task decomposition, code writing optimization, matrix calculation acceleration library selection, and cpu compilation acceleration to reduce software running time. In the end, the software running time on the satellite computing board is in compliance with the constraints on board, reducing from 49 minutes to 15 minutes.

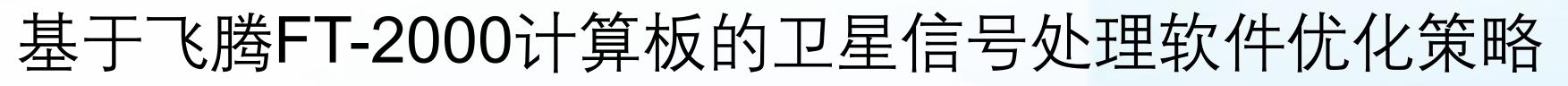

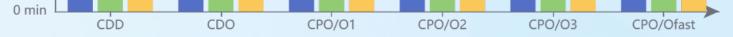

## The operation flow of satellite signal processing **software:** The space-based supercomputing platform (TZ load) receives signal data from the signal receiving load through the LVDS communication protocol. The data preprocessing module converts the received binary data into a yml file, which is mainly used to store complex number matrices. After that, the signal data processing module performs the algorithmic processing of the data. Finally, the data processing module transmits the results to the spaceborne computer through the CAN bus protocol, and the spaceborne computer downloads the results to the ground.

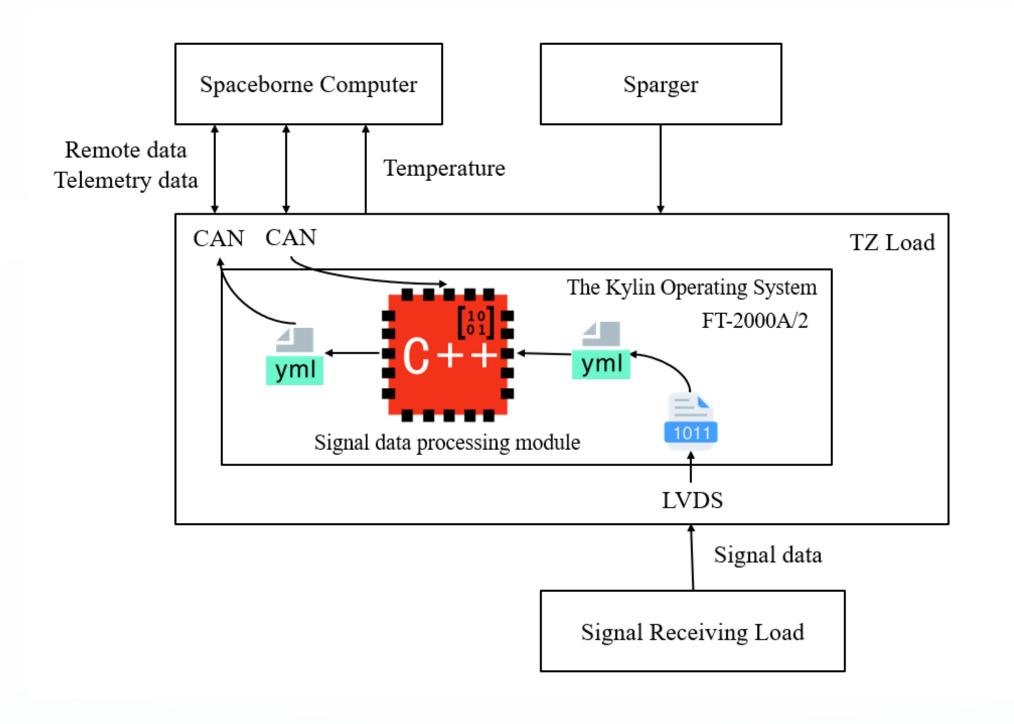

## **Optimization Strategy:** We have

adopted four code optimisation and runtime acceleration methods for on-star applications :

✓ Analysis of code architecture Global architecture optimization ✓ Task decomposition

- **Task Decompositon**

- **Code Compilation Optimization**  $\bullet$

- Matrix Calculation Acceleration **Library Selection**

- **Compilation Optimization**  $\bullet$

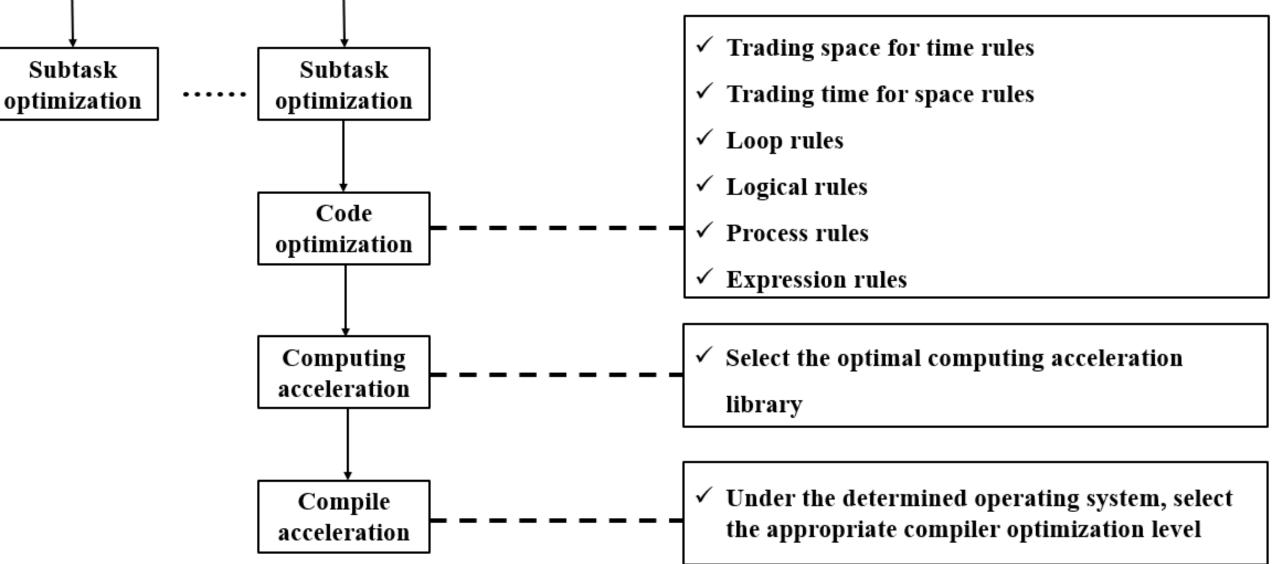

**Experiment one:** the first experiment is carried out in the environment of a ground workstation. This paper use the signal processing software written in MATLAB language, and in C++ language, and the software after different optimization steps to run on the ground workstation to process 1G single-precision signal data. we also check the effect of the optimization.

Subtask

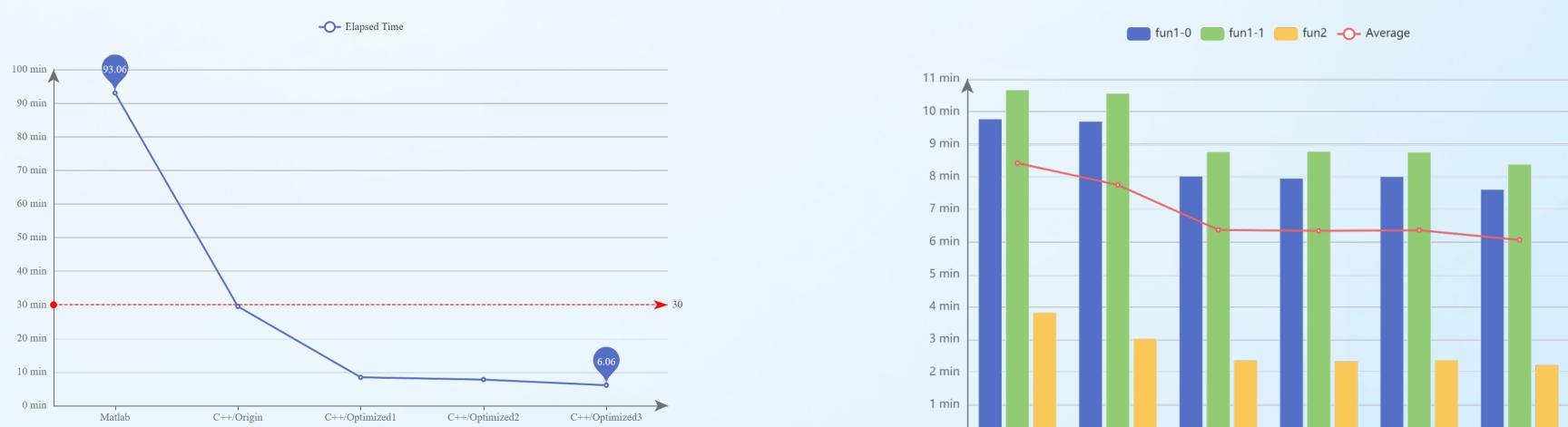

**Experiment two:** After passing the experiment one, we migrated the optimized code to the Feiteng computing board for experimentation, and the running results are shown in the table.

|                | Fun1-0 | Fun1-1 | Fun2 |

|----------------|--------|--------|------|

| Result(min)    | 19.79  | 19.27  | 5.86 |

| Avg CPU(%)     | 27.2   | 26.3   | 26.6 |

| Peak Memory(%) | 44.5   | 44.1   | 45.1 |

| Avg Memory(%)  | 19.9   | 19.6   | 44.5 |

**Conclusion:** The unavailability of hardware acceleration methods on satellites and the limitation of computing resources of computing boards have become constraints for many signal processing applications that cannot run smoothly in orbit. These constraint problems are solved by the application software optimization strategy proposed in this paper, which applied task decomposition, code optimization, matrix calculation library selection, and compilation optimization methods. The proposed optimization strategy is worth using for reference for the signal processing, image processing and other application software optimization on the embedded platforms, where a large number of matrix calculations are involved in, because the embedded systems have similar computational resource constraints.